אינטל

אינטל אכן התקשתה בצורה משמעותית עם מעברם לצומת 10nm והדיווחים אף העלו כי חברת השבבים שימרה אותו לחלוטין, אך לבסוף קיבלנו מפת דרכים מעודכנת על אירוע האדריכלות של אינטל שעזרה להקל על חלק מהחששות. מפת הדרכים המתוקנת הציגה את סאני קוב שעתידה לרשת את סקיילייק בשנת 2019 ואכן הייתה בצומת 10nm.

סאני קוב ממש חשובה מאוד עבור אינטל מכיוון שעד כה החברה עשתה שימוש חוזר בליבות ישנות על מוצרים רעננים שלא ממש ירדו בקהילה. ואז יש איום מתמשך שמקורו ב- Ryzen של AMD ובארכיטקטורת הזן שלהם. AMD הצליחה לסגור את פער הביצועים בצורה משמעותית למדי במוצרים מתחרים והם גם תימחרו את השבבים שלהם בצורה מאוד תחרותית וגרמו להרכב של אינטל להראות רע. זה משפיע גם על עסקי השרתים של אינטל מכיוון ש- AMD תשחרר שבבי EPYC רומא שרת בהמשך השנה וגם דליפות ראשוניות מציע ביצועים נהדרים. שבבי קסאון הבנויים על ארכיטקטורת סאני קוב בהחלט יעזרו לאינטל להתחרות במרחב השרת בו הם היו כוח דומיננטי די זמן מה.

סאני קוב - שדרוג המיקרו-ארכיטקטורה הגדול ביותר של אינטל בזמן האחרון

בשל עיכובים ב -10 ננומטר אינטל נאלצה להישאר עם 14 ננומטר יותר מהצפוי. זה הביא להשקות מרעננות רבות, וכתוצאה מכך אגם קאבי, אגם הקפה ואגם הוויסקי. היו שיפורים פה ושם אבל שום דבר משמעותי מדי. סוף סוף סאני קוב תשנה את זה.

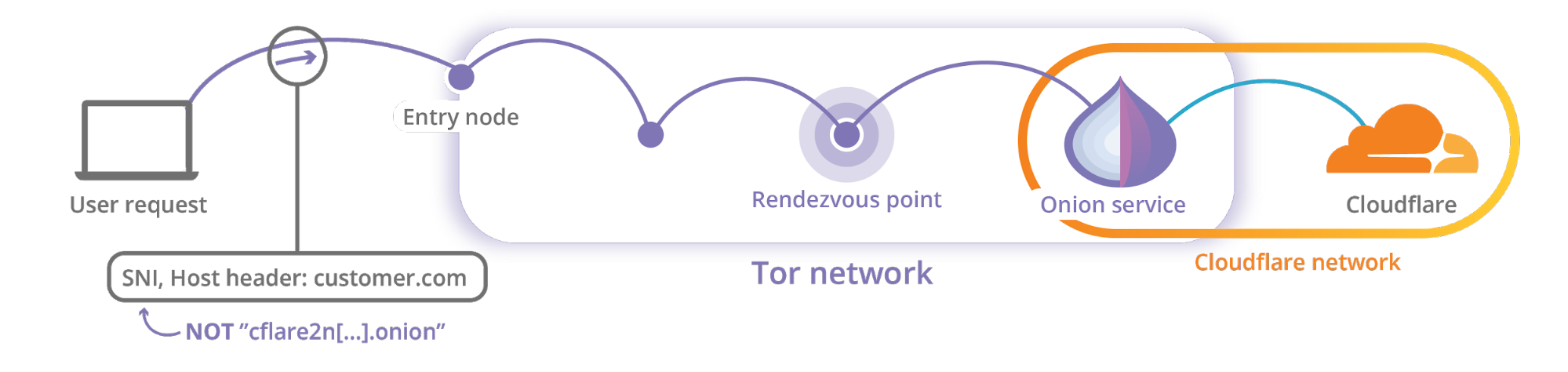

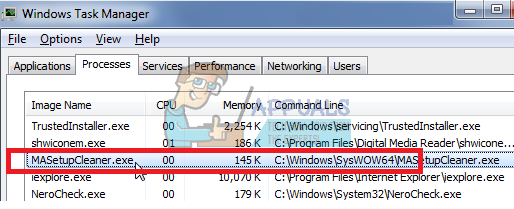

מקור שיפורים חזיתיים 'רחבים יותר' - אננאדטק

מקור שיפורים חזיתיים 'עמוקים יותר' - אנאנדטק

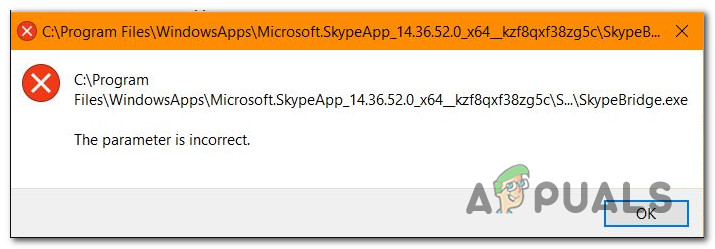

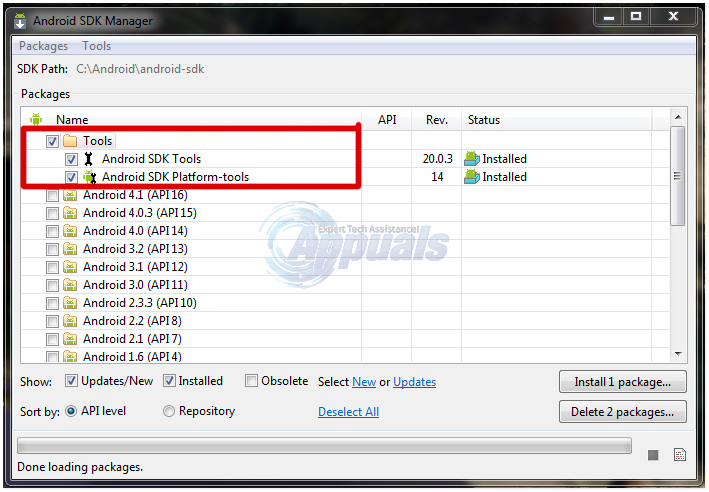

מלבד עלייה בתפוקת ה- IPC הגולמית יחולו גם שיפורים כלליים. אינטל ביום האדריכלות שלהם הציגו את השיפורים בהקשר של 'רחב יותר' ו'עמוק יותר '. ל- Sunny Cove יש מטמון L1 ו- L2 גדול יותר, ויש לו גם הקצאות ברוחב 5 במקום 4. יציאות הביצוע מוגדלות, ועוברות מ- 8 ל- 10 ב- Sunny Cove.

שיפור IPC

אינטל לייקפילד SoC

SoC זה יהיה אחד המוצרים הראשונים שמשתמשים בליבות של סאני קוב, והוא גם הראשון להשתמש טכנולוגיית אריזות תלת מימד Foveros . אינטל חשפה לאחרונה פרטים נוספים על Lakefield SoC הקרובה שלהם ולמעשה יש הרבה מה להתרגש.

ביסודו של דבר מדובר במעבד היברידי המשתמש בערימה כדי להתאים לחלקים שונים בחבילה אחת. ערימה על חבילה היא למעשה די נפוצה עבור SoCs ניידים אך אינטל משתמשת בגרסה מעט מגוונת. במקום גשרים מסיליקון, Foveros tech משתמשת במוצרי F-T-F בין הערימות. אריזות Foveros מאפשרות גם להציב את הרכיבים במתכות שונות. בדרך זו אינטל יכולה למקם ליבות בעלות ביצועים גבוהים המכונים ליבות סאני קוב על תהליך 10nm המתקדם יותר, רכיבים אחרים יכולים להיות ממוקמים על חלק התהליך 14nm של השבב. שכבות DRAM ממוקמות מעל כאשר המעבד והשבב של GPU מגיעים מתחתיו ואז מכשיר הבסיס ממוקם עם מטמון ו- I / O.

דבר מעניין נוסף כאן הוא היישום של גָדוֹל . LITTLE עם חומרת x86 . זה בעצם השימוש בשני סוגים של מעבדים לסוגים שונים של משימות, הליבות החזקות משמשות למשימות עתירות משאבים ובינתיים ליבות ההספק הנמוכות משמשות לתפקוד רגיל. לייקפילד משתמשת בעיצוב של חמישה ליבות, עם ארבע ליבות הספק נמוכות יותר (Atom) וליבה אחת בעלת הספק גבוה (Sunny Cove). תכנון זה מיושם מכיוון שהוא משפר את היעילות מכיוון שביצועים קלים יותר להרחבה בין אשכולות הליבה השונים. לייקפילד היא ללא ספק SoC המכוונת למכשירים ניידים, מחשבים ניידים קומפקטיים ו- ultrabooks, אך בעיקר התגובה של אינטל לקוואלקום שמתכוננת לשחרר ARC SoC משלהם למכשירי Windows.

תגים אינטל